Co to jest?

Jak to działa?

Pamięć RAM od środka

Pamięci ulotne umożliwiające zarówno zapis, jak i odczyt danych, nazywane są tradycyjnie pamięciami o dostępie swobodnym (ang. Random Access Memory). W komputerach stosuje się je jako element pośredni pomiędzy szybkimi rejestrami procesora a wolnymi dyskami twardymi. Jak zobaczymy, również pamięci RAM dzielą się na dwie główne kategorie: szybkie i drogie pamięci statyczne (ang. Static RAM) oraz wolniejsze i tańsze pamięci dynamiczne (ang. Dynamic RAM).

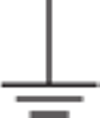

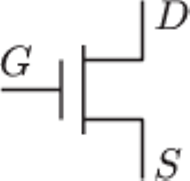

Rys. 1 Bramka NAND (Not AND)

Komputery operują na sygnałach w postaci napięcia elektrycznego pomiędzy punktem a wyróżnionym potencjałem, tzw. masą. Odpowiednio wysokie napięcie jest uznawane za stan logiczny „1”, a odpowiednio niskie za stan „0”. Dzięki temu, zamiast myśleć o napięciach, można wznieść się na wyższy poziom abstrakcji i rozumować w kategoriach wartości logicznych. Układy, które pracują na takich stanach, nazywamy układami cyfrowymi. Ich podstawowymi elementami składowymi są bramki logiczne – urządzenia, które realizują pewną prostą funkcję logiczną (np. NOT, AND, OR, NAND – Rys. 1). Pamięci w układach cyfrowych da się zbudować, korzystając wyłącznie z bramek logicznych.

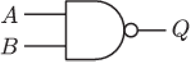

Rys. 2 Zatrzask SR

Pamięć statyczna – podejście pierwsze

Aby układ zbudowany z bramek logicznych mógł zapamiętać bit informacji, musi wystąpić sprzężenie zwrotne, czyli część wyjść musi zostać poprowadzonych z powrotem do wejść. Taka sytuacja ma miejsce w układzie nazywanym zatrzaskiem SR, który można zbudować z wzajemnie połączonych dwóch bramek NAND (Rys. 2).

Stany wysokie na obu wejściach

nazywamy stanem

nieaktywnym. Proszę sprawdzić, że dla takich wejść wyjścia układu mają

dwa możliwe stany stabilne:

nazywamy stanem

nieaktywnym. Proszę sprawdzić, że dla takich wejść wyjścia układu mają

dwa możliwe stany stabilne:

oraz

oraz

Te

poziomy logiczne utrzymywane są przez bramki tak długo, jak długo podłączone

jest zasilanie. Uznajemy, że oznaczają one zapisany w układzie bit informacji,

odpowiednio 1 i 0.

Te

poziomy logiczne utrzymywane są przez bramki tak długo, jak długo podłączone

jest zasilanie. Uznajemy, że oznaczają one zapisany w układzie bit informacji,

odpowiednio 1 i 0.

Odczyt bitu możliwy jest w każdej chwili z linii wyjściowych. Natomiast aby

zaktualizować dane, należy odpowiednio manipulować wejściami. W celu

zapisania jedynki ustawiamy na pewien czas

Wymusza

to przejście wyjść układu do umownej jedynki logicznej. Gdy

następnie, ustawiając

Wymusza

to przejście wyjść układu do umownej jedynki logicznej. Gdy

następnie, ustawiając

wrócimy do stanu nieaktywnego, ta

wartość pozostanie zapamiętana w układzie. Analogicznie poprzez

wrócimy do stanu nieaktywnego, ta

wartość pozostanie zapamiętana w układzie. Analogicznie poprzez

zapisujemy zero. Na wejściach może również

wystąpić

zapisujemy zero. Na wejściach może również

wystąpić

ale wtedy

ale wtedy

Nie wiąże się z tym

żadna wartość bitu danych, więc stan ten jest traktowany jako logicznie

zabroniony.

Nie wiąże się z tym

żadna wartość bitu danych, więc stan ten jest traktowany jako logicznie

zabroniony.

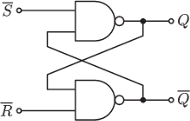

Rys. 3 Bramka NOT

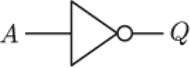

Rys. 4 Tranzystor NMOS w zastosowaniach cyfrowych przypomina sterowany napięciem

przełącznik: gdy

to

to

jest zwarte z

jest zwarte z

a dla

a dla

– rozwarte,

tranzystor nazywamy wtedy odpowiednio otwartym i zamkniętym.

– rozwarte,

tranzystor nazywamy wtedy odpowiednio otwartym i zamkniętym.

Pamięć statyczna – podejście drugie

W praktyce komórki pamięci statycznej realizuje się nieco inaczej. Poprzez

połączenie linii wejściowych i wyjściowych oraz użycie bramek NOT

(Rys. 3) zamiast NAND można uprościć strukturę komórki i zmniejszyć

liczbę linii sterujących. Schemat komórki pamięci przedstawia rysunek

5. Dwie bramki NOT wzajemnie oddziałują na swoje wejścia. Mogą

być w dwóch stabilnych stanach, które rozróżniają wartości bitu.

W układzie znajdują się dodatkowo dwa tranzystory dostępowe (Rys. 4)

sterowane linią

Przez większość czasu zachodzi

Przez większość czasu zachodzi

wtedy bramki są odcięte od stanów na liniach danych

wtedy bramki są odcięte od stanów na liniach danych

i

i

Dzięki temu do linii danych można podłączyć wiele komórek

pamięci.

Dzięki temu do linii danych można podłączyć wiele komórek

pamięci.

Odczyt danych odbywa się przez otwarcie tranzystorów linią

Wtedy linie danych przyjmują wartości

Wtedy linie danych przyjmują wartości

gdy zapisany był

bit 1, lub

gdy zapisany był

bit 1, lub

gdy zapisane było 0. Aby zapisać dane, należy

ustawić odpowiednie stany na liniach danych, a następnie otworzyć

tranzystory. Rezystancja zastępcza tranzystorów dostępowych i tranzystorów

wchodzących w skład bramek NOT jest tak dobrana, aby wartości na liniach

danych wymusiły stan bramek, a układ zapamiętał nowy bit informacji.

gdy zapisane było 0. Aby zapisać dane, należy

ustawić odpowiednie stany na liniach danych, a następnie otworzyć

tranzystory. Rezystancja zastępcza tranzystorów dostępowych i tranzystorów

wchodzących w skład bramek NOT jest tak dobrana, aby wartości na liniach

danych wymusiły stan bramek, a układ zapamiętał nowy bit informacji.

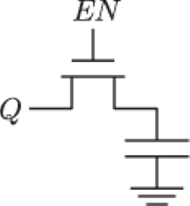

Rys. 6 Komórka DRAM

Pamięć dynamiczna

Innym pomysłem na zapis bitu informacji jest reprezentowanie go jako stanu naładowania kondensatora. Naładowany kondensator oznacza logiczne 1, a rozładowany – 0. Komórka takiej pamięci zawiera tylko dwa elementy: tranzystor dostępowy i kondensator połączony z masą (Rys. 7).

Aby wpisać bit informacji do pamięci, ustawia się odpowiedni stan linii

a następnie otwiera tranzystor, ustawiając

a następnie otwiera tranzystor, ustawiając

Gdy po

pewnym czasie kondensator już się naładuje bądź rozładuje, zgodnie

z napięciem na

Gdy po

pewnym czasie kondensator już się naładuje bądź rozładuje, zgodnie

z napięciem na

można z powrotem zamknąć tranzystor

dostępowy.

można z powrotem zamknąć tranzystor

dostępowy.

Odczyt danych jest równie prosty. Wystarczy otworzyć tranzystor i odczytać

stan pamięci z linii

Linia danych

Linia danych

w praktyce łączy

wiele wyjść komórek pamięci i jest dość długa. Niestety, okazuje

się, że jej pojemność pasożytnicza jest większa niż pojemność

kondensatora komórki pamięci. Przez to przy każdym odczycie kondensator

rozładowuje się, a właśnie otrzymany bit danych trzeba zapisać od

nowa.

w praktyce łączy

wiele wyjść komórek pamięci i jest dość długa. Niestety, okazuje

się, że jej pojemność pasożytnicza jest większa niż pojemność

kondensatora komórki pamięci. Przez to przy każdym odczycie kondensator

rozładowuje się, a właśnie otrzymany bit danych trzeba zapisać od

nowa.

Sytuację dodatkowo komplikuje fakt, że nawet gdy tranzystor jest zamknięty, to przepływa przez niego niewielki prąd. Rezystancja tranzystora, choć bardzo duża, jest skończona. Kondensator powoli się rozładowuje, a dane należy odświeżyć, żeby nie zostały utracone. Polega to na przeprowadzeniu odczytu, po którym nastąpi powtórny zapis bitu. Pamięć musi być wyposażona w dodatkowy układ, który co pewien czas odświeża całą zawartość pamięci. Właśnie ze względu na konieczność odświeżania ten typ pamięci został nazwany pamięcią dynamiczną.

Parametry i zastosowanie

Pamięci można porównać pod względem kosztu przechowywania bitu informacji, szybkości działania i zużycia mocy.

Standardowa komórka SRAM składa się z sześciu tranzystorów, natomiast komórka DRAM – z jednego tranzystora i kondensatora. Prostsza budowa powoduje, że komórki DRAM można gęściej upakować na płytce krzemowej, a ponadto pamięć ta jest wyraźnie tańsza.

Jednak pamięć dynamiczna jest wolniejsza niż statyczna. Wynika to z kilku czynników. Po pierwsze, w trakcie cyklu odświeżania zawartości pamięci nie jest możliwy dostęp do pamięci. Po drugie, zapis i odczyt danych wymagają ładowania lub rozładowywania kondensatora w komórce pamięci, co zajmuje niezerowy czas. Operacje na pamięci statycznej również wymagają przeładowania pewnych pojemności pasożytniczych, ale znacznie mniejszych. Dane są dostępne niemal natychmiast po aktywowaniu tranzystorów dostępowych. Dokładne czasy dostępu do pamięci zależą od realizacji układu. W przybliżeniu wynoszą 10 ns i 60 ns odpowiednio dla pamięci statycznej i dynamicznej. Dla porównania: w czasie 10 ns nowoczesne procesory mogą wykonać około 20 instrukcji, a światło przebywa trzy metry.

Pod względem zużycia mocy znowu wygrywa pamięć statyczna. Utrzymywanie stanu pamięci statycznej wymaga zasilania bramek NOT. Najwięcej mocy zużywane jest jednak na dostępy do pamięci, co powoduje, że tracona moc jest proporcjonalna do częstotliwości dostępów. Pamięć dynamiczna wymaga większej mocy, ponieważ aktywnie utrzymuje dane w kondensatorach, odświeżając ich zawartość. Kondensatory cyklicznie ładują się i rozładowują, co zużywa prąd.

Komórki pamięci statycznej i dynamicznej różnią się strukturą wewnętrzną i parametrami. Przekłada się to na ich zastosowania. Pamięć dynamiczną stosuje się tam, gdzie potrzebna jest pojemna, w miarę szybka pamięć – np. w kościach pamięci operacyjnej. Większe zużycie mocy ogranicza zastosowania tego typu pamięci w układach zasilanych bateryjnie. Natomiast pamięć statyczna jest używana tam, gdzie ważny jest szybki dostęp do danych, czyli m.in. jako pamięć podręczna procesora i bufory routerów, a także w małych urządzeniach elektronicznych, w których liczy się prostota układu obsługującego pamięć.

to

to

jest zwarte z

jest zwarte z

a dla

a dla

– rozwarte,

tranzystor nazywamy wtedy odpowiednio otwartym i zamkniętym.

– rozwarte,

tranzystor nazywamy wtedy odpowiednio otwartym i zamkniętym.